SDRAM是如何“提速”的?

各位同学大家好,欢迎继续做客电子工程学习圈,今天我们继续来讲这本书,硬件系统工程师宝典。

上篇我们了解了FLASH可分为NOR FLASH和NAND FLASH,NOR FLASH一般用于代码运行及擦除或编程较少的场合,NAND FLASH用于擦除、编程速度快,但是不用于直接运行代码的场合。今天我们来讲一讲SDRAM的相关知识。

SDRAM

SDRAM指同步动态随机存储器,同步指的是Memory工作需要同步时钟,内部命令发送和数据传输都以同步时钟为基准;动态指的是存储阵列要不断地刷新保证数据不丢失;随机指的是数据不是线性存储而是自由指定进行数据读/写。

SDRAM的内部存储结构如下图所示:

SDRAM内部的存储结构

我们在进行取址操作时,需要依次获取Bank数、行地址、列地址,从而找到要读取或写入的数据。在系统设计时,Memory的容量如下计算:

例如,某SDRAM的行地址信号为A0~A12,列地址信号线为A0~A9,A11,数据信号线为DQ0~DQ7,位宽为8,Bank数是4,则Memory的容量是213*211*4*8bit=512Mbit。

那么,我们在选型时,要确认Bank数、行地址数、列地址数是否和CPU匹配,Memory的位宽是否支持。

DDR SDRAM

DDR SDRAM(Double Data Rate SDRAM)是指双倍速率同步动态随机存储器。其中双倍指的是DDR内存除了像SDRAM一样在时钟上升期进行数据传输外,在时钟下降期也可以进行数据传输,因此DDR内存更快。

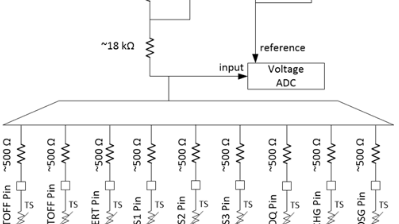

DDR SDRAM的Memory容量计算和SDRAM是一样的,DDR SDRAM在数据采样上不再依赖于时钟信号采样,而是采用DQS(数据选通信号,Data Strobe)进行采样。在写操作时,数据由CPU发往DDR,DDR数据接收端利用DQS的边沿对DQ进行采样;读操作时,数据由DDR发送给CPU,在接收端的存取器利用DQS的边沿对DQ采样。DDR SDRAM的数据采样依赖DQS信号,而地址、命令和控制信号等单端信号仍采用时钟信号采样。

DDR2 SDRAM

DDR2 SDRAM简称DDR2,是第二代双倍数据率同步动态随机存取存储器(Double-Data-Rate Two Synchronous Dynamic Random Access Memory)。DDR2的实际工作频率是DDR的两倍,得益于DDR2内存拥有两倍于DDR内存的预读取能力,如下图所示:

DDR和DDR2预读取能力的对比

除了预读取能力的提升,DDR2 SDRAM既可以采用单端DQS信号,也可采用差分DQS信号,使用差分信号以减少信号串扰的影响。另外,DDR2 SDRAM采用SSTL-1.8电平,在相同存储容量和相同数据传输率的情况下,DDR2具有更低的功耗。

DDR3 SDRAM

DDR3是在DDR2基础上采用的新型设计,与DDR2 SDRAM相比具有功耗、发热量较小、工作频率更高等优势。

DDR3的内部是一个存储阵列,类似一张表格,将数据“填”进去,如下图所示:

DDR3存储阵列的等效表格

那么,我们芯片寻址就跟检索表格一样,先指定一个行(Row),再指定一个列(Column),就可以准确地找到所需要的单元格(存储单元),这个表格对应的就是逻辑Bank(Logical Bank)。图中黑格的位置表示根据寻址命令B1、R2、C6确定的位置,寻址的流程也就是先指定Bank地址,再指定行地址,然后指定列地址,最终确定寻址单元。

DDR3和DDR2的信号种类是一样的,其中DDR3不再支持单端DQS数据选通信号,全部采用差分数据选通信号,DDR3对DQS与Clock没有严格的时序要求,而DDR2对DQS与Clock有严格的时序要求。DDR3供电采用1.5V,接口电平逻辑满足SSTL_1.5V。

DDR4 SDRAM

内存颗粒的演变如下图所示:

内存颗粒的演变

可以看出,DDR4在2014年开始崛起,在2015年后开始迅速占领市场。DDR4内存的运行频率提升至2133~4266MHz,电压降低至1.2V、1.1V。另外,与DDR3相比,DDR4的接口引脚增加了,ACT_n命令激活输入信号,BG0-BG1用于选择哪个Bank被激活,PAR输入命令和地址信号的奇偶校验,ALERT_n报警的输入和输出信号,VPP用于DRAM激活的2.5V供电引脚等。

另外,整理了一些电子工程类的资料,分享给大家,目前有模拟电路、单片机、C语言、PCB设计、电源相关、FPGA、EMC、物联网、Linux相关学习资料,还有针对大学生的资料包,后续还会有更多资料分享给大家,助力大家学习,成就梦想~

博主福利:点击链接免费获取电子工程类学习资料「链接」

FLASH搭上SDRAM,并不是你想象的那样不用布等长!

文|原创:卧龙会 上尉Shonway

FLASH在布线的时候,大家都知道只要靠近主控芯片,只要连接上就可以了,并不需要做等长。但有时并不是大家想象的那样。一起来看看这个实例。

小编近来在工作中遇到一个问题。在一个项目中用到的一个主控芯片芯片是QFP封装,它采用的是数据线共用的策略。也就是说FLASH与SDRAM共用数据线。这样FLASH与SDRAM就形成了一个分叉。

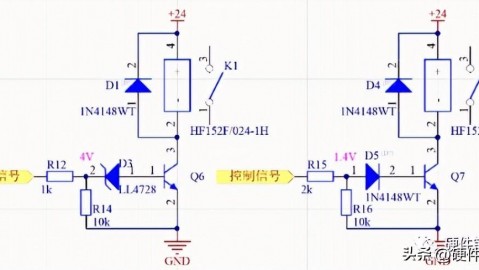

小编就觉得SDRAM速率也并那没么高。做个T形分叉连接也没事。原创微信公众号:卧龙会IT技术。并不用采用菊花链形式。这样主控芯片到FLASH与SDRAM的线也短一点。拓朴结构就采用了如下图所示形式

在主控芯片与SDRAM这一端的做了等长处理。这个大家都知道,SDRAM信号虽不是那么高速,但还是做等长比较保险一点。但FLASH这一侧,小编就想当然的就没有做等长处理,而是采用一般的FLASH布局布线策略,靠近主芯片然后直接连上完事。

做了一板出来,调试没问题。小编觉得这是小事,肯定没问题。做了这么久的高速设计,连个SDRAM都搞不定,还叫PCB LAYOUT工程师吗?哈哈,洋洋得意了一把。

第一板没问题,第二板由于硬件,软件方面需要修改,又改了一稿。这部分就不改了。还有其它项目这部分也是按此布线策略布线。好像都没问题。

一天,软件工程师遇到一个问题,说从主芯芯片从FLASH这端读出来写入SDRAM时,出现了数据读取错误,而在另一个项目上没问题。怎么回事?

然后就查问题了,看了一下板,有组USB线从FLASH的下面穿过,是不是这个原因,导致有干扰。于是乎用刀割掉USB线。调试还不行。那怎么回事呢?最后就考虑到等长问题上了。SDRAM是等长的,没问题?唯一的一点是FLASH没有等长。按照经验来说,FLASH速率很低,不用严格等长。那怎么会有问题呢。

如果FLASH等长有问题,那个另外一个项目同样的布线策略为什么就没问题。后来就推断,可能是在从FLASH读数据后立即写入SDRAM过程中。原创微信公众号:wlh-it。FLASH这边由于不等长各数据线产生的时序差传到更高速的SDRAM时产生了时序不匹配问题。以及各数据线由于在FLASH这一侧的不等长产生的阻抗突变不一致,反射不一致等等种种原因导致数据从FLASH读取写入SDRAM时产生了数据错误。

如下图所示

唯一办法只能是再做一稿把FLASH这一侧也布等长线。来验证是不是这个问题。于是就修改完再去做一稿,拿回来让软件工程师验证,没问题了。

总结:一般高速电路板,FLASH跟高速信号肯定是分开的。不会低速与高速共用数据线。所以FLASH因为是低速,不用做等长。但FLASH与高速信号SDRAM在数据线共用的时候,还是要注意一下这个等长问题。FLASH也需要尽量等长。以避免SDRAM侧产生数据错误。也只有SDRAM才会与FLASH共用数据线。DDR2,DDR3等等的肯定不会与FLASH共用数据线。

更多精彩:

微信|微博:卧龙会IT技术

相关问答

arm CPU集群 如何启动?启动方式(1)norflash:2MB,从norflash的0地址处开始运行第一条代码,所以代码一定要放在norflash的最前端(2)nandflash:128MB,但是nandflash没有参...

我在stm32外加了sram和 flash 怎样让程序从片外的 flash 启动?方法一:从flash旧扇区,取出1k数据到ram,放到flash新的扇区;从flash旧扇区,取出第2个1k数据到ram,放到flash新的扇区;重复至取完,然后再擦除flash旧扇...方....

ddr与 flash 区别?Flash:电源关闭数据保留。结合了ROM和RAM的长处,不仅具备电子可擦除可编程(EEPROM)的性能,还不会断电丢失数据同时可以快速读取数据(NVRAM的优势)。DDR=Doubl...

norflash和ddr区别?NORFlash是一种非易失闪存技术,是Intel在1988年创建。DDR的全称为DoubleDataRateSDRAM,也就是双倍速率的SDRAM,SDRAM在一个CLK周期传输一次数据,...

显卡怎么刷bios超频?前段时间,QQ时代给自己的TNT成功的更新了BIOS,一时兴起便写作了一篇“TNT换脑记”,这篇文章在DIYclub和《电脑自作DIY》杂志上发表之后,博得了许多朋友的关注...

flash 芯片参数含义?FLASH是闪存芯片的意思,1M/2M/4M是他的容量。ROM只读存储器RAM随机存储器CDROM光驱SDRAM过去的一种内存类型,2000年前后的主流。flash芯片是低功耗低.....

NURAM是什么?NURM:高密度非易失性存储器两个专业名词—非易失性存储器和易失性存储器非易失性存储器:指掉电后在相当长时间内依然能有效保存数据的存储器。如EEPROM,EP...

NAND 与ROM有什么不同-ZOL问答我的PPC有8G的NAND但是ROM只有128MB,我想问在WM系统中NADN和ROM的使用功能一样吗,或者说NADN能够当作是ROM使用吗?在待机状态系系统会像SDMMC那样切断储存器电...

arm 缓存 地址范围?在ARM处理器中,缓存地址范围通常被称为“cacheline”,它是一个连续的内存块,它的大小通常是32字节到256字节之间。缓存行的大小可能会因特定的ARM处理器而异...

固态硬盘SATA和mSATA有什么区别 - 171****3911 的回答 - 懂得Sata硬盘,就是标准的2.5寸笔记本硬盘,体积比较大,绝大多数笔记本只能替换掉主硬盘。速度快了,但容量较小。mSATA(mini-SATA)是迷你版本SATA接口,外...